# OCTEON TX2 Infrastructure Processor Family

## Announcement of Next Generation Infrastructure Processors

OCTEON Fusion®

### OCTEON TX2 Announcement

- Industry-leading data path performance up to 200Gbps for networking and security applications

- Up to 5 100G MACs integrated in the OCTEON TX2 infrastructure processor leading to significant TCO advantage

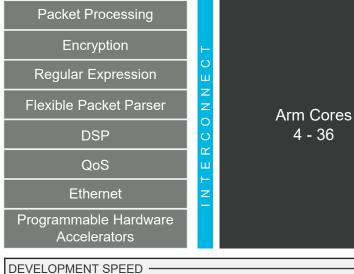

- OCTEON TX2 Infrastructure Processor family combines 4 to 36 Armv8based architecture cores with configurable, programmable hardware accelerator blocks

- Fully virtualized SoC architecture Second line of text example

- Cores, I/O and all data-plane acceleration engines are fully virtualized

### OCTEON TX2 Announcement

- Target Markets:

- Enterprise Networking / security

- 5G wireless infrastructure

- Service provider / multi-access Edge compute

- Cloud / Data Center

### **Highest Performance Infrastructure Processor Family**

## A Long History of Compute Innovation

## Announcement of Next Generation Infrastructure Processors

- This is the standard bullet slide

- Keep bullet points brief

- Use line spacing to clearly separate each point

- Second line of text example

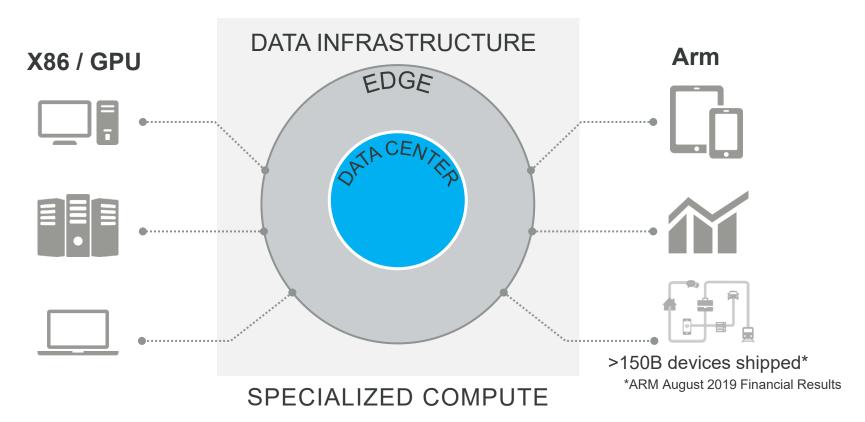

## New Horizons - New Solutions

## From the Core to the Edge – Technology Leadership

| DATA    | A CENTER | CARRIER | ENTERPRISE     | EDGE | THINGS |

|---------|----------|---------|----------------|------|--------|

|         |          | End-to  | -end SECURITY  |      |        |

|         |          | Pack    | ket Processing |      |        |

| Compute |          |         |                |      |        |

|         |          | Sign    | al Processing  |      |        |

## What is a Marvell Infrastructure Processor?

Specialized compute, Marvell's heritage

Highly programmable & configurable blocks intelligently connected

High-performance datapath

Power-optimized

Interconnected CPU cores

Optimized Arm cores with Marvell interconnect know-how

Leading-edge process technology

Arm strategic relationship

DEVELOPMENT SPEED > 4

POWER > 4

PERFORMANCE > 4

PROGRAMMABILITY > 5

Higher is better

Infrastructure Processor: Leading Compute and Data Plane

High-end firewall Crypto offload

Routers and switches

Control / data, crypto offload

Macro / micro BTS

Transport layer and crypto

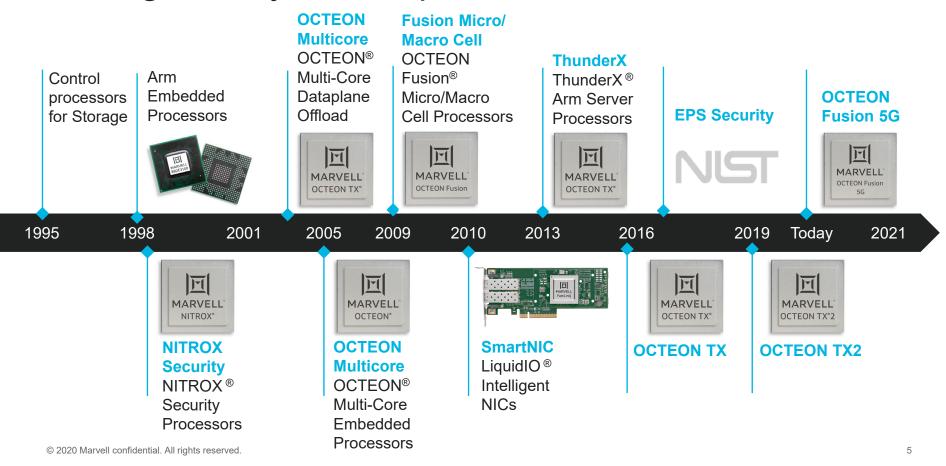

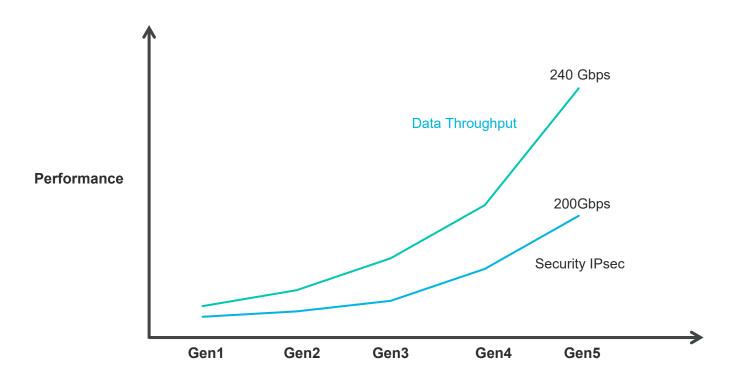

## Marvell Infrastructure Processor Timeline

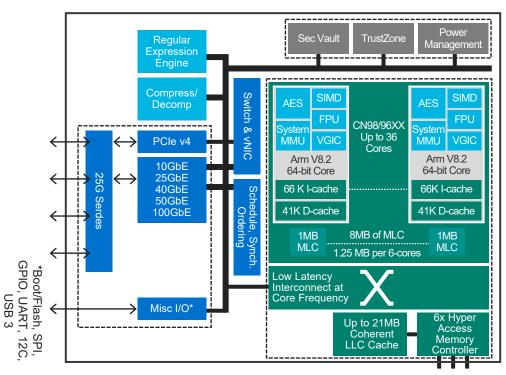

## OCTEON TX2 Infrastructure Processor: CN98/96xx

4C A72 20 Gbps NOW

12-18C ARMv8.2 50 Gbps NOW

18-24C ARMv8.2 100 Gbps NOW

24-36C ARMv8.2 200 Gbps Q2'2020

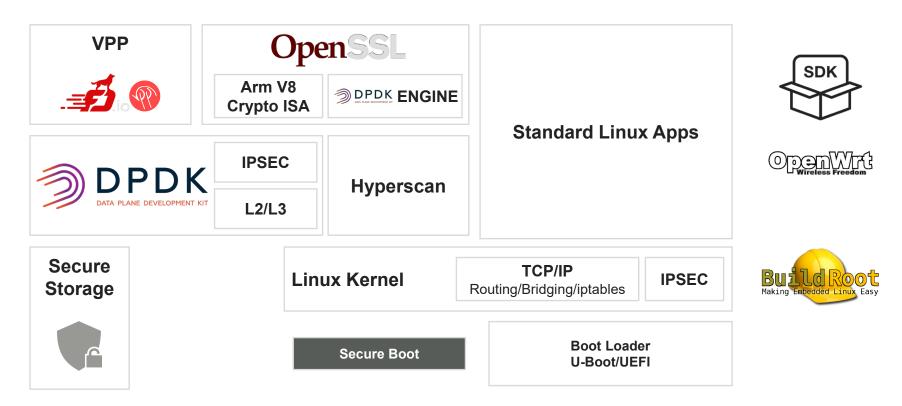

Unified software development environment supporting standard Linux, DPDK, containers & virtualization

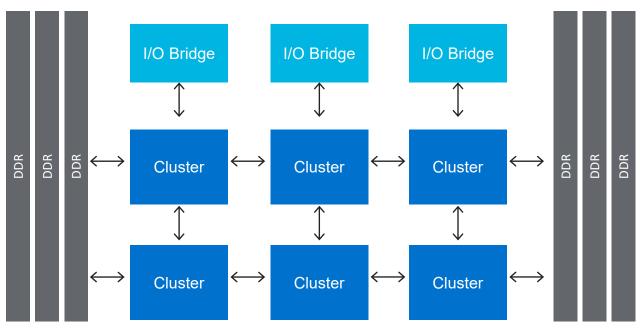

### OCTEON TX2 Infrastructure Processor: CN98/96xx

Introducing the industry's highest performing Infrastructure Processor family

- Highest Compute (SPECINTRate) SOC in its class

- Multi-core scaling w/ low latency interconnect

- Rich I/O

- HW acceleration for packet processing, encryption

6x 72b DDR4-3200

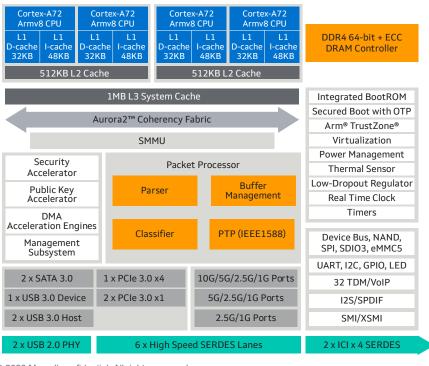

## CN9130 – Best Performance/Watt Processor Targeting SOHO/SMB

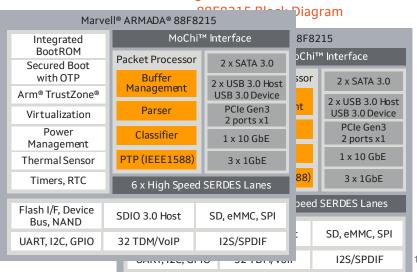

CN9130 block diagram

- CN913X Up to 4 cores (20 Gbps)

- Supports up to 18 SERDES lanes

- <10W power consumption</p>

#### 88F8215 Block Diagram

## OCTEON TX/TX2: Portfolio

| Metric                         | CN913X                   | CN83XX         | CN92XX          | CN96XX          | CN98XX             |

|--------------------------------|--------------------------|----------------|-----------------|-----------------|--------------------|

| Cores                          | 4                        | 8-24           | 12-18           | 18-24           | 30-36              |

| Max Freq                       | 2.2G                     | 2.0G           | 2.0G            | 2.4G            | 2.4G               |

| Cache (MLC, LLC)               | 2MB                      | 8MB            | 5MB, 8MB        | 5MB, 14MB       | 8MB, 21MB          |

| DDR4                           | 1@2400MTS                | 2@2100MTS      | 2@3200MTS       | 3@3200MTS       | 6@3200MTS          |

| Ethernet                       | Up to 3<br>x10G+6x1/2.5G | 12x10G         | 4x25G, 8x10G    | 3 x100G/12x25G  | 5 x100G/20x25G     |

| Max PPS                        | 15Mpps                   | 60Mpps         | Up to 50Mpps    | Up to 120Mpps   | Up to 220Mpps      |

| IP FWDing                      | Up to 25G                | Up to 60G      | Up to 80G       | 120G-140G       | 200G-240G          |

| IPSEC (Gbps)                   | Up to 15G                | 30Gbps         | 50Gbps          | 100Gbps         | 200Gbps            |

| Serdes                         | Up to 18x 10G            | 22x 10G        | 32x 16G/25G     | 32x 16G/25G     | 48-56 16G/25G      |

| PCI-e Physical<br>Interface/VF | Up-to 18x v3/8           | 24 lanes v3/64 | 24 lanes v4/256 | 24 lanes v4/256 | 32 lanes v4/512-1K |

| Estimated TDP                  | 9W-14W                   | 30W-55W        | 45W-65W         | 55W-80W         | 80W-120W           |

| AVAILABLE                      | NOW                      | NOW            | NOW             | NOW             | Q2'2020            |

## Unified Software Development Environment

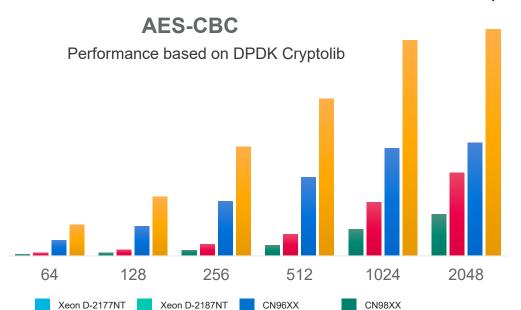

## Marvell Security Acceleration Performance Advantage

Infrastructure Processor with Crypto accelerator Performance vs. software implementation with QAT

| Crypto<br>Requirement<br>(1KB Packet) | Intel Xeon | Marvell<br>Infrastructure<br>Processor |

|---------------------------------------|------------|----------------------------------------|

| 50G                                   | *128W      | 50W                                    |

| 100G                                  | **155W     | 75W                                    |

| 200G                                  | ***300W    | 135W                                   |

Packet size \*\*\*Marvell Estimate

Marvell Measured/Estimates, Intel http://static.dpdk.org/doc/perf/DPDK\_19\_08\_Intel\_crypto\_performance\_report.pdf

## Proof Point: Security Appliance Example

### Intrusion Protection | Firewall | IPSEC

#### **Higher Performance**

| Intrusion Prevention | 12G | 50G  |

|----------------------|-----|------|

| Firewall             | 50G | 200G |

| IPSEC                | 6G  | 100G |

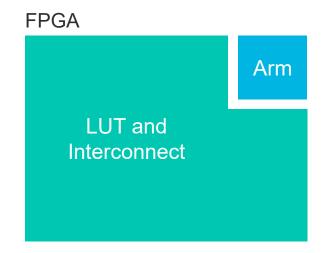

## Proof Point: Network Visibility and Analysis Appliance

CPU with FPGA

Infrastructure Processor

Xeon - 2187NT

FPGA

IIII

Ethernet

Power: 235W Price: 3X+ Marvell

CN96XX: 24 Core

Ethernet

Power: <75W Price: 1X

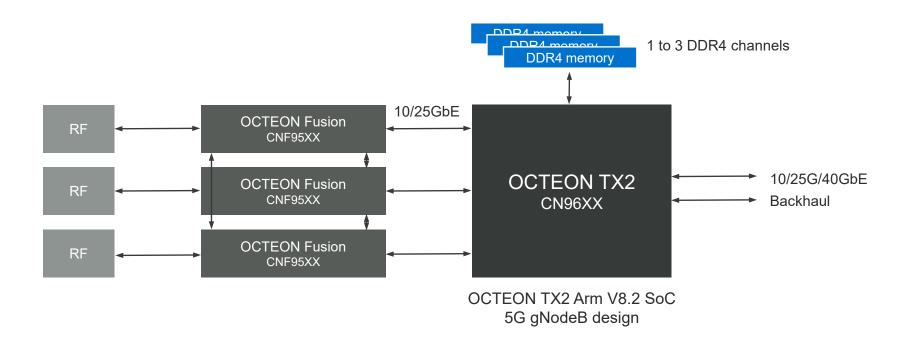

## Proof Point: 5G Macro Base Station

## Summary

- Industry-leading data path performance up to 200Gbps for networking and security applications

- Up to 5 100G MACs integrated in the OCTEON TX2 infrastructure processor leading to significant TCO advantage

- OCTEON TX2 Infrastructure Processor family scales 4 to 36 Arm v8-based architecture cores with configurable, programmable hardware accelerator blocks

### **Highest Performance Infrastructure Processor Family**

## Traditional Data Infrastructure Compute Options

**CPU** only

Arm / X86 Compute

Fixed Arm

ASIC

Gates

```

DEVELOPMENT SPEED > 5

POWER > 2

PERFORMANCE > 2

PROGRAMMABILITY > 5

```

| DEVELOPMENT SPEED | > 3 |

|-------------------|-----|

| POWER             | → 2 |

| PERFORMANCE       | → 3 |

| PROGRAMMABILITY   | > 5 |

| DEVELOPMENT SPEED | → 1            |

|-------------------|----------------|

| POWER             | > 5            |

| PERFORMANCE       | > 5            |

| PROGRAMMABILITY   | → <sub>1</sub> |

© 2020 Marvell confidential. All rights reserved.

22

## OCTEON TX2 Value Proposition: The Best of Both Worlds

3 I/O bridges (each 1+Tbps) for 200Gbps of Data-plane processing

CN98xx architecture

Essential technology, done right™